めっき方法

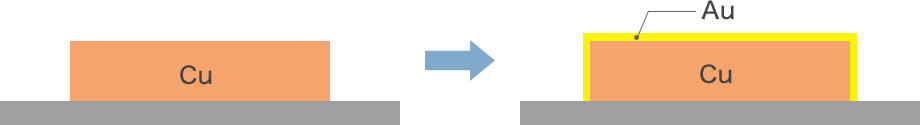

- DIG

-

銅上に置換金めっきを直接する方法、direct immersion goldの略。Niめっきを省いているためENIGに比べファインピッチ対応が可能。層構成はCu-Au。

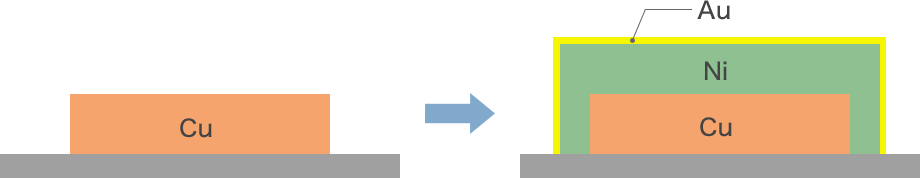

- ENIG

-

銅上に無電解ニッケルめっき及び置換金めっきをする方法、electroless nickel immersion goldの略。層構成はCu-Ni-Au。

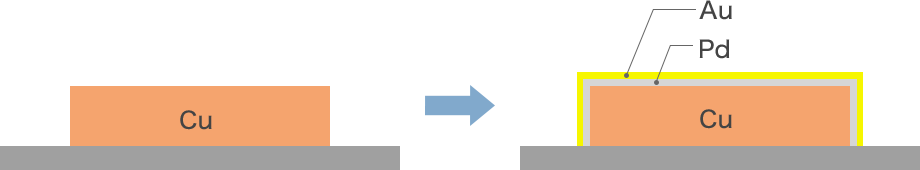

- EPIG

-

銅上に無電解パラジウムめっき及び置換金めっきをする方法、electroless palladium immersion goldの略。層構成はCu-Pd-Au。

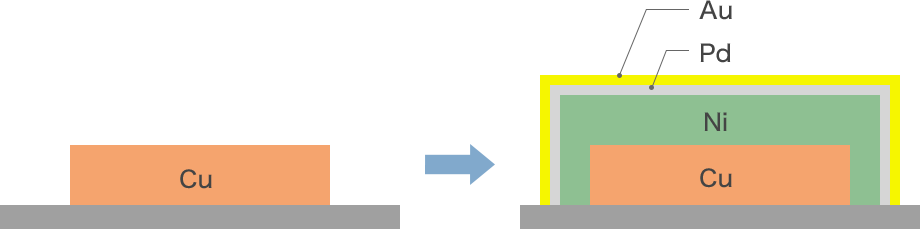

- ENEPIG

-

銅上に無電解ニッケルめっき、無電解パラジウムめっき及び置換金めっきをする方法、electroless nickel electroless palladium immersion goldの略。層構成はCu-Ni-Pd-Au。

- 電解めっき(電気めっきともいう)

- 金属又は非金属表面に金属を電気化学的に析出させる方法。

- 無電解めっき

- 外部電源を使用せず化学反応によりめっきする方法。

- 置換めっき、還元めっき

- 無電解めっき法の分類。金属のイオン化傾向の違いを利用する置換法と、還元剤を利用する還元法とに大別される。

- 軟質金めっき、硬質金めっき

- 金めっきの純度が高い(99.9%以上)ものを軟質金めっきといい、合金成分を入れ純度を下げて(99.9%以下)硬度を高めたものを硬質金めっきという。

- バンプめっき

- 半導体の電極に小さな金属突起(バンプ)を形成するめっき方法。バンプ形成により電極と基板をワイヤレスで直接接合できるため、電子部品を小型にすることができる。

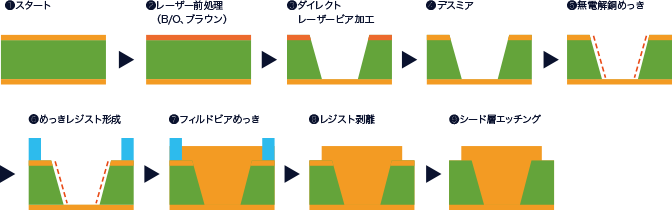

- ビアフィルめっき

- 回路の層数が二つ以上になると、導体層の間を電気的に接続する必要がある。その接続に使用するホールをビアホールと言い、ビアホールを埋めるめっき方法。

- PPF

- リードフレームめっき方法。Pre Plated Leadframeの略、Pdめっきの場合はPd-PPF(Palladium Pre Plated Leadframe)と記載するのが一般的。

めっき工程

- 前処理

- めっき工程において基板をめっき浴に入れる前の諸工程。脱脂、エッチング、酸洗浄工程が該当。

- 後処理

- めっき工程において基板をめっき浴に入れた後の諸工程。めっき工程、封孔処理等が該当。

- 封孔処理

- 省金化に伴い薄膜化するとピンホール(微小な孔)ができてしまう。めっき後に封孔処理剤で処理することで防錆効果を高める。

- 脱脂

- 素地に付着している油脂性の汚れを除去して清浄にする操作。

- エッチング

- 金属又は非金属表面を化学的又は電気化学的に腐食する方法。樹脂上にめっきする場合には、酸化剤を含む液に樹脂を浸せきし、表面粗化と化学的変化を同時に行う方法。

めっき関連用語

- マイクロスイッチ

- 接点の間隔が狭く瞬時に切り替わる機構により開閉動作する小型スイッチ。瞬時に接点が切り替わるので、アークの持続時間が短く、小型でも大電流が流すことが可能。

- コネクター

- 複数の電子部品又はプリント基板を電気的に接続するための接続端子。

- プリント基板

- コンデンサーなどの電子部品を実装する配線回路形成された基板の総称。

- リジッド基板

- 柔軟性のない絶縁体基材を用いた回路基板。

- フレキシブル基板

- 柔軟性があり、弱い力で繰り返し変形させることが可能であり、変形した場合にもその電気的特性を維持する特性をもつ基板。リジット基板と比較し加工性に優れるため、複雑な形状加工が可能である。

- リードフレーム

- 半導体パッケージの内部配線として使われる薄板の金属のことで、外部の配線との橋渡しの役目を果たしており、半導体パッケージの大部分に使われる。

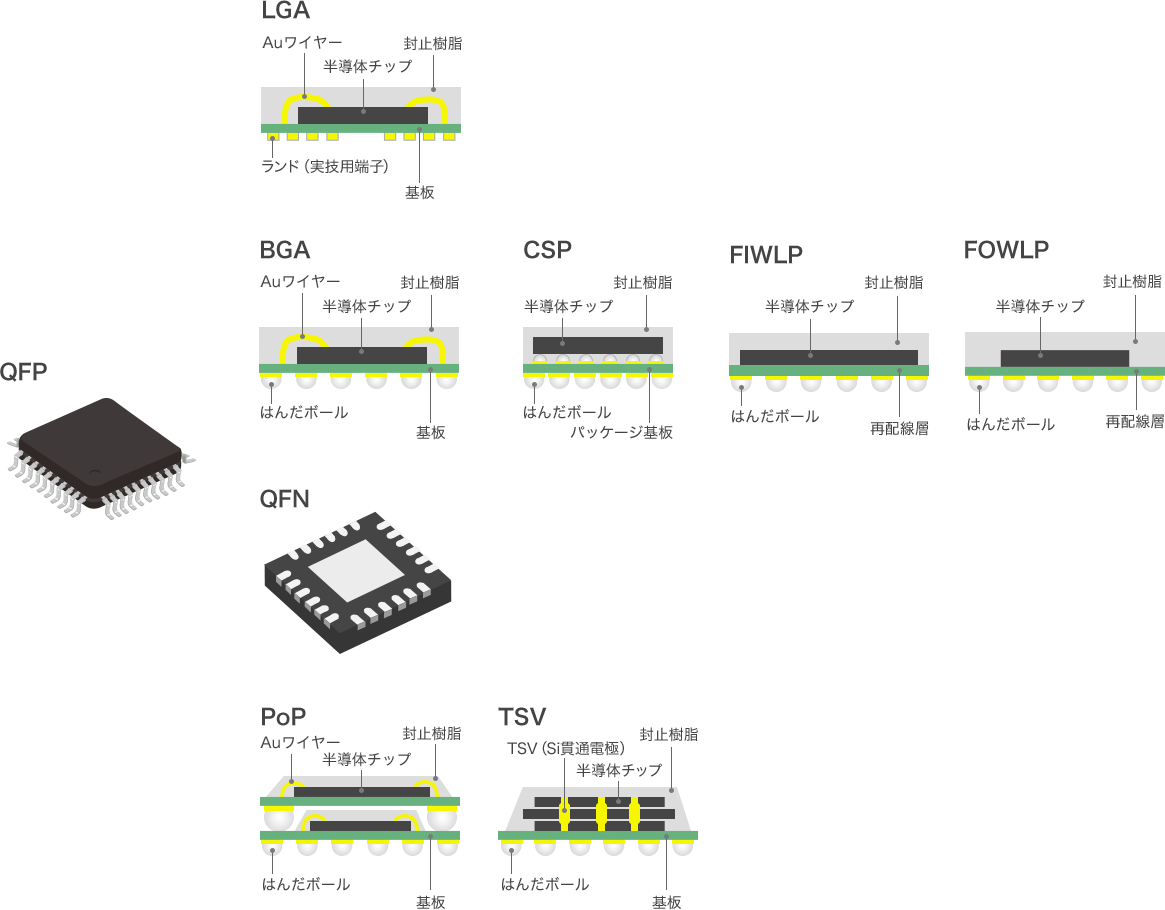

- リードフレームパッケージ変遷図

-

- QFP

-

Quad Flat Packageの略。パッケージの4方向全ての側面から外部端子が出ている表面実装型リードフレームパッケージ。

- QFN

-

Quad Flat Non-Lead Packageの略。パッケージの4方向全ての外部端子がパッケージの裏面に配置されている表面実装型リードフレームパッケージ。

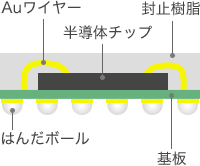

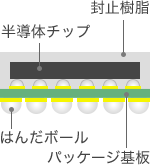

- BGA

-

パッケージの電極上にはんだボールを配置したもので、プリント配線板との接続に用いられる。Ball Grid Arrayの略。

- CSP

-

Chip Size Packageの略。ICのチップとほぼ同じ大きさの超小型パッケージのこと。CSPを使用することで、セットの基板実装面積を大幅に削減できる。

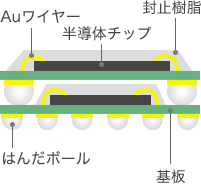

- PoP

-

Package on Packageの略。小型、薄型電子機器の普及につれて高まる基板の高密度化・省スペース化の要求に伴い、PoP実装が省スペース化を実現するための一技術として適用されている。

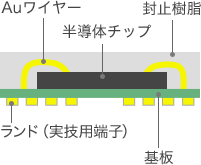

- LGA

-

ICパッケージの底面に銅などの電極パッドを配列して端子とした基板。Land Grid Arrayの略。

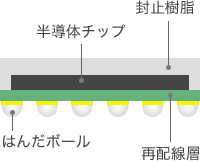

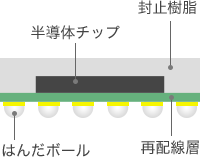

- FIWLP

-

Fan In Wafer Level Packageの略。半導体チップとプリント配線基板の間をつなぐ再配線層を、半導体工程を使って作るウエハーレベルパッケージの一種。パッケージ面積と半導体チップ面積が同じ。

- FOWLP

-

Fan Out Wafer Level Packageの略。半導体チップとプリント配線基板の間をつなぐ再配線層を、半導体工程を使って作るウエハーレベルパッケージの一種。パッケージ面積が半導体チップ面積より大きく、チップの外側まで端子を広げること(fan out)ができる。チップ面積と比べて端子数が多い用途でも採用できる。

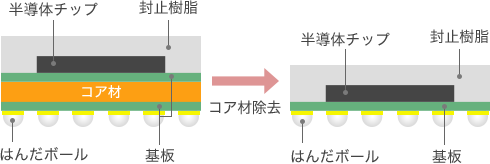

- コアレス基板

-

コア材(銅張積層板)を用いない構成の半導体パッケージ用基板。

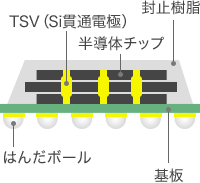

- TSV

-

半導体のシリコン貫通電極のことでThrough-Silicon Viaの頭文字を取った名称。

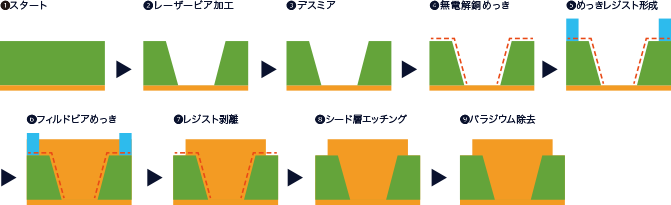

- SAP基板

-

非回路部分にあらかじめレジストを形成しておき、シード層(パラジウムなど)のある回路部分のみをめっきで回路形成した基板、サップはSemi Additive Processの略。

- MSAP基板

-

SAPがシード層を形成する必要があるのに対して、MSAPは極薄Cu箔の上にめっきで配線を形成するという違いがあり、微細配線を比較的作りやすいとされる、Modified Semi Additive Processの略。

- Protecting Agent

-

特定の金属に選択的に吸着し、電子を供与又は吸引する効果によって、めっき反応や皮膜物性をコントロールする一連の有機化合物。

- 貴金属

- 一般には高価な金属をいうが、電極電位が高くイオン化しにくく、したがって空気中で加熱しても酸化されにくい金属である。

- 卑金属

- イオン化傾向が水素より大きく、空気中で熱したりすると容易に酸化される金属を指す。アルミニウム、鉄、ニッケル、錫などがこれに属する。

- ドライフィルムレジスト

- 銅上に回路を形成するためのフィルム状のレジスト材料。めっき処理中に表面を一時的に保護した後、アルカリなどで溶解除去可能。

- ソルダーレジスト

- 銅配線の回路パターンを保護する絶縁膜となる材料。電気的接続をとる接点以外にはんだ(ソルダー)が付着してショートするのを防止する。

- ワイヤーボンディング

- ICチップとリードフレームやプリント基板とを金属線(金、アルミニウムなど)で接続する方法。